ESD protection for transmission interfaces

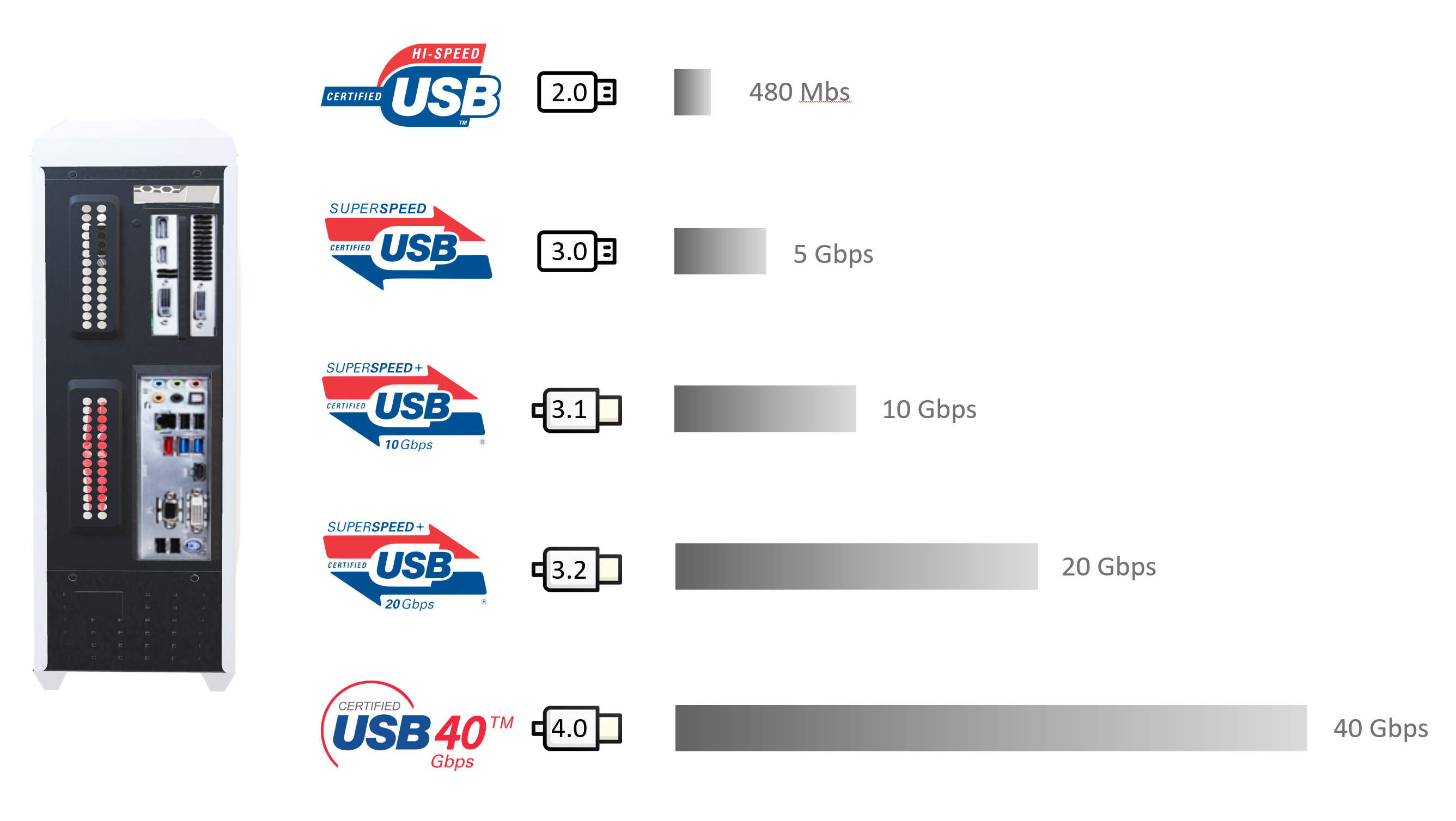

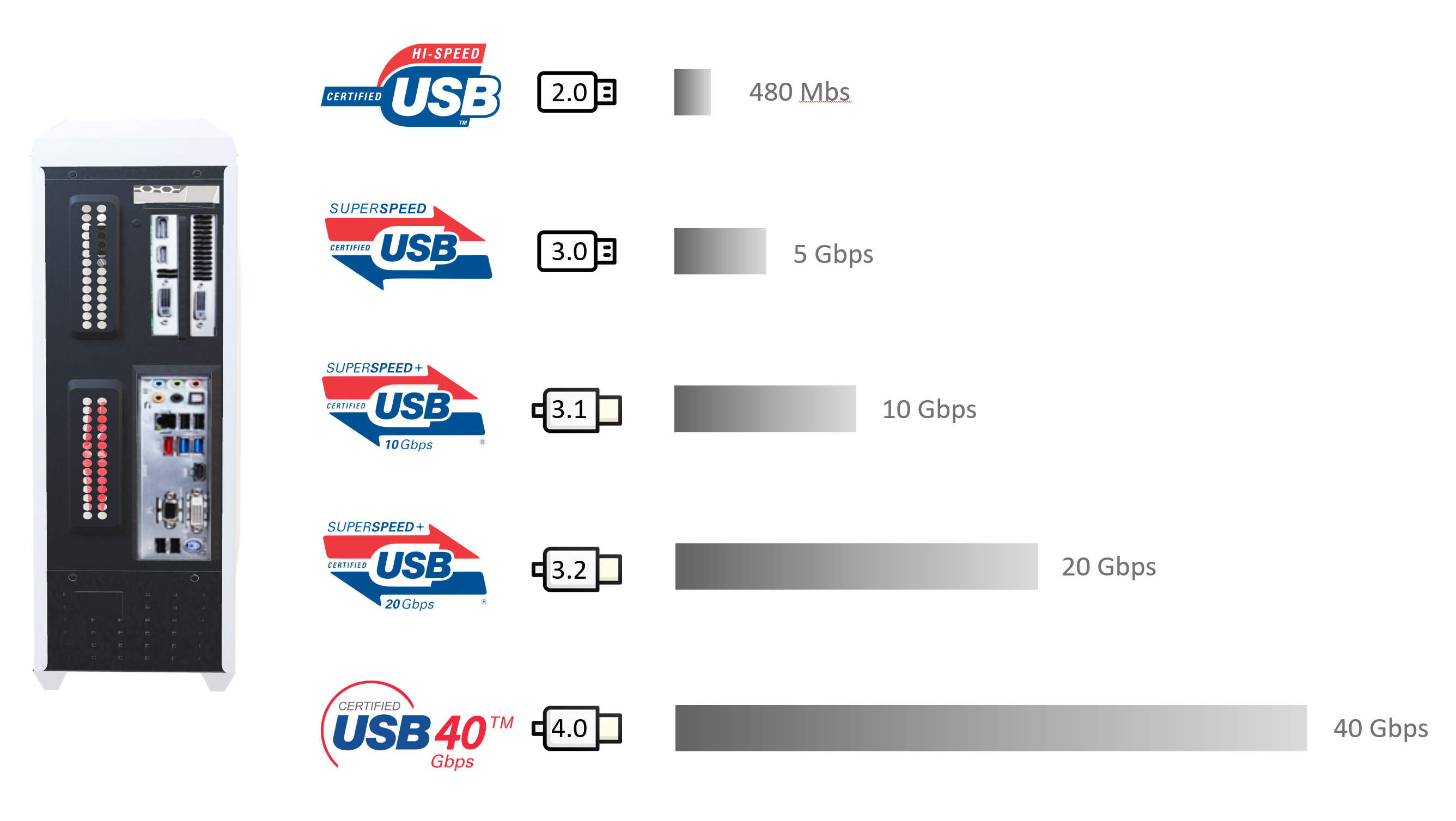

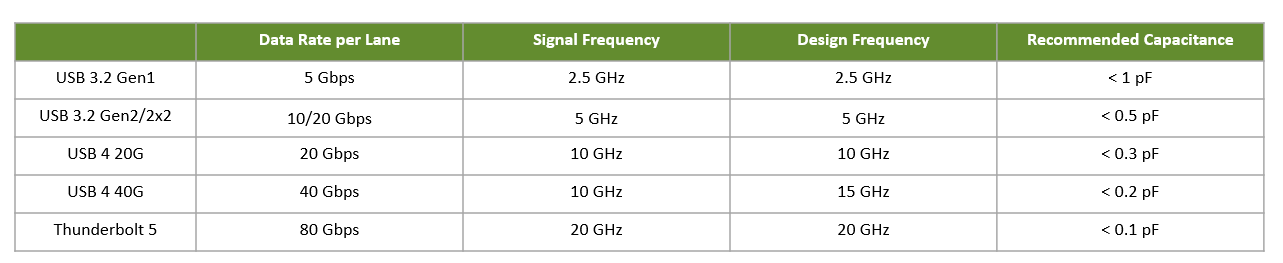

Super speed transmission interfaces have specific requirements regarding signal loss and spatial constraints, necessitating components with low capacitance and compact size.

1.Use low-capacitance components to maintain signal integrity.

2.Ensure IEC 61000-4-2 compliance (≥8 kV contact discharge).

3.Lower clamping voltage offers better protection.

4.Meet signal quality requirements in insertion loss and eye diagram tests.

Frequency and capacitance estimation formula:

1.Higher signal frequency requires lower capacitance.

2.To maintain signal integrity at high frequencies, ESD protection components must have ultra-low capacitance.

3.As frequency increases, the acceptable capacitance decreases to avoid signal distortion, insertion loss, and eye diagram degradation.

4.Typical design rule: the cutoff frequency of the RC filter formed by the ESD component should exceed the signal frequency by at least 2–3×.

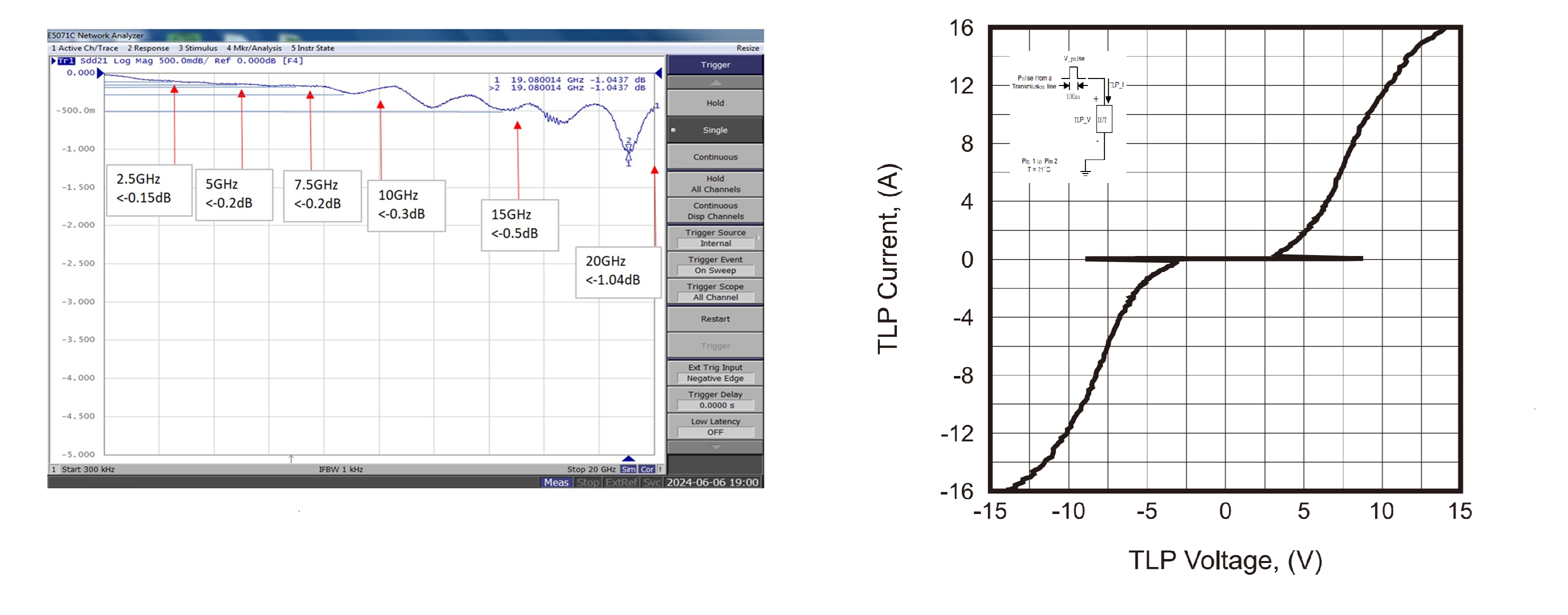

Comchip offers the CPDWZ5V0SBP-HF series with lower clamping voltage and reduced capacitance, optimized for various transmission interfaces. These components demonstrate excellent performance in both eye diagram analysis and S21 insertion loss testing. The ultra-low capacitance model, CPDWZ5V0P-HF, features a capacitance as low as 0.08 pF.

Part Number

Status

AEC-Q

Uni/Bi

PPP(W)

VRWM(V)

Vc(V)

IPP(A)

Cj(pF)

ESD(kV)

Package

Active

-

Bi

40

5

20

2

0.08

15

CSP0603-2L

Active

-

Bi

20

5

8

2.5

0.15

10

CSP0603-2L

Active

-

Bi

30

5

14

2

0.2

15

0201/DFN0603

Active

-

Bi

14

3.3

3.5

4

0.25

12

CSP0603-2L

Active

-

Bi

72

1.5

8

9

0.26

20

CSP0603-2L

Active

-

Bi

62

5

8.8

7

0.26

15

CSP0603-2L

Active

-

Bi

40

5

8

5

0.29

18

CSP0603-2L

Active

-

Bi

27

5

3.8

7

0.4

26

CSP0603-2L

Active

-

Bi

34

3.3

4.5

7.5

0.45

22

CSP0603-2L

Active

-

Bi

42

5

7

6

0.45

12

CSP0603-2L

Active

-

Bi

75

5

9

10

0.48

16

CSP0603-2L

Active

-

Bi

15

5

5

3

0.5

17

0201/DFN0603-2L

Cookie

This website uses cookies, including third-party cookies, to provide you with the best browsing experience. For more information, please visit our Privacy and Cookie Policy. By continuing to browse or closing this notice, you acknowledge that you have accepted our Terms of Use.

Welcome to the “COMCHIP Technology Website” (hereinafter referred to as "this Website").

To ensure that you can use the services and information provided by this Website with peace of mind, we hereby explain our Privacy Policy to protect your rights and interests. Please read the following carefully: