傳輸介面的 ESD 保護

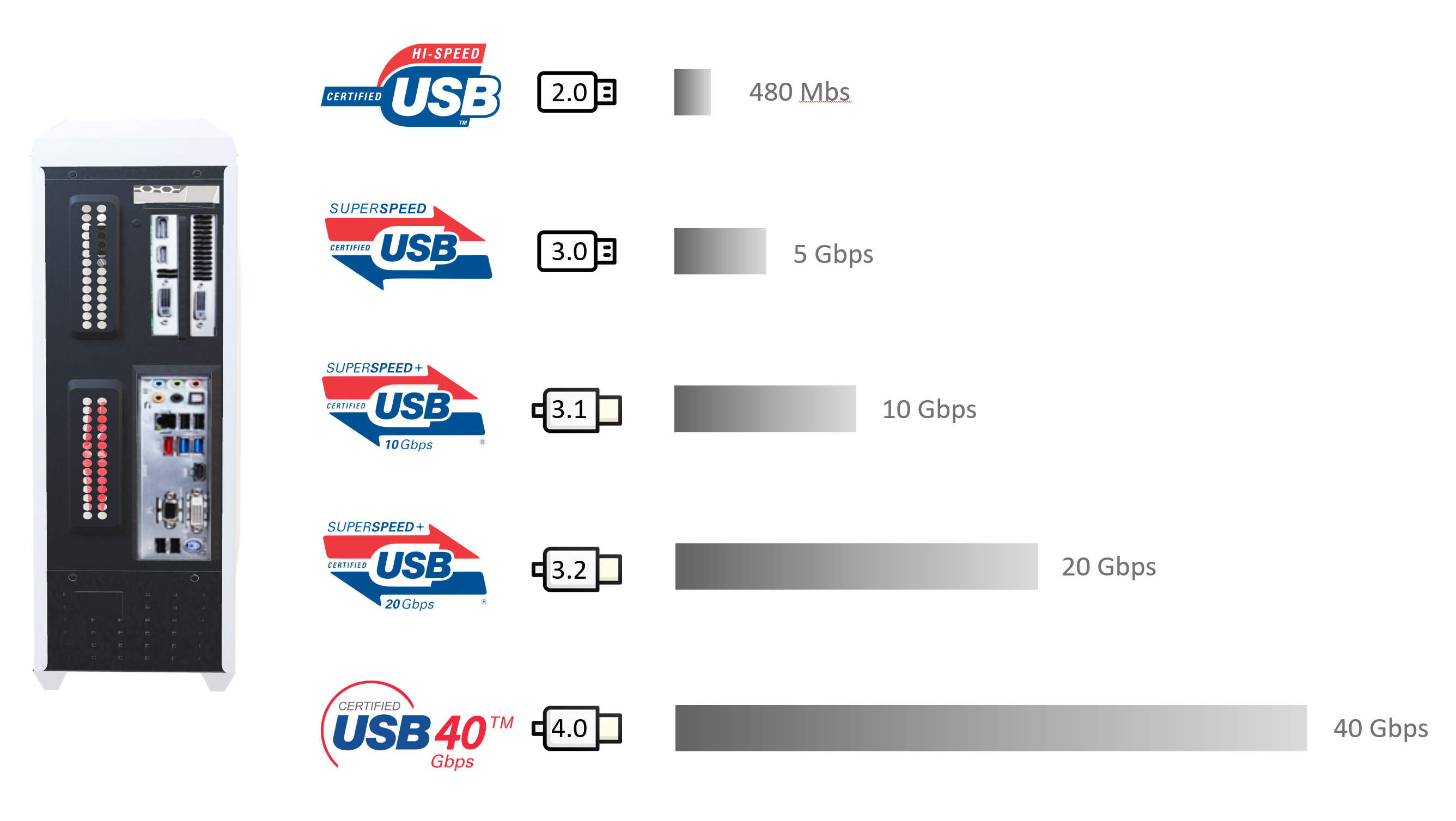

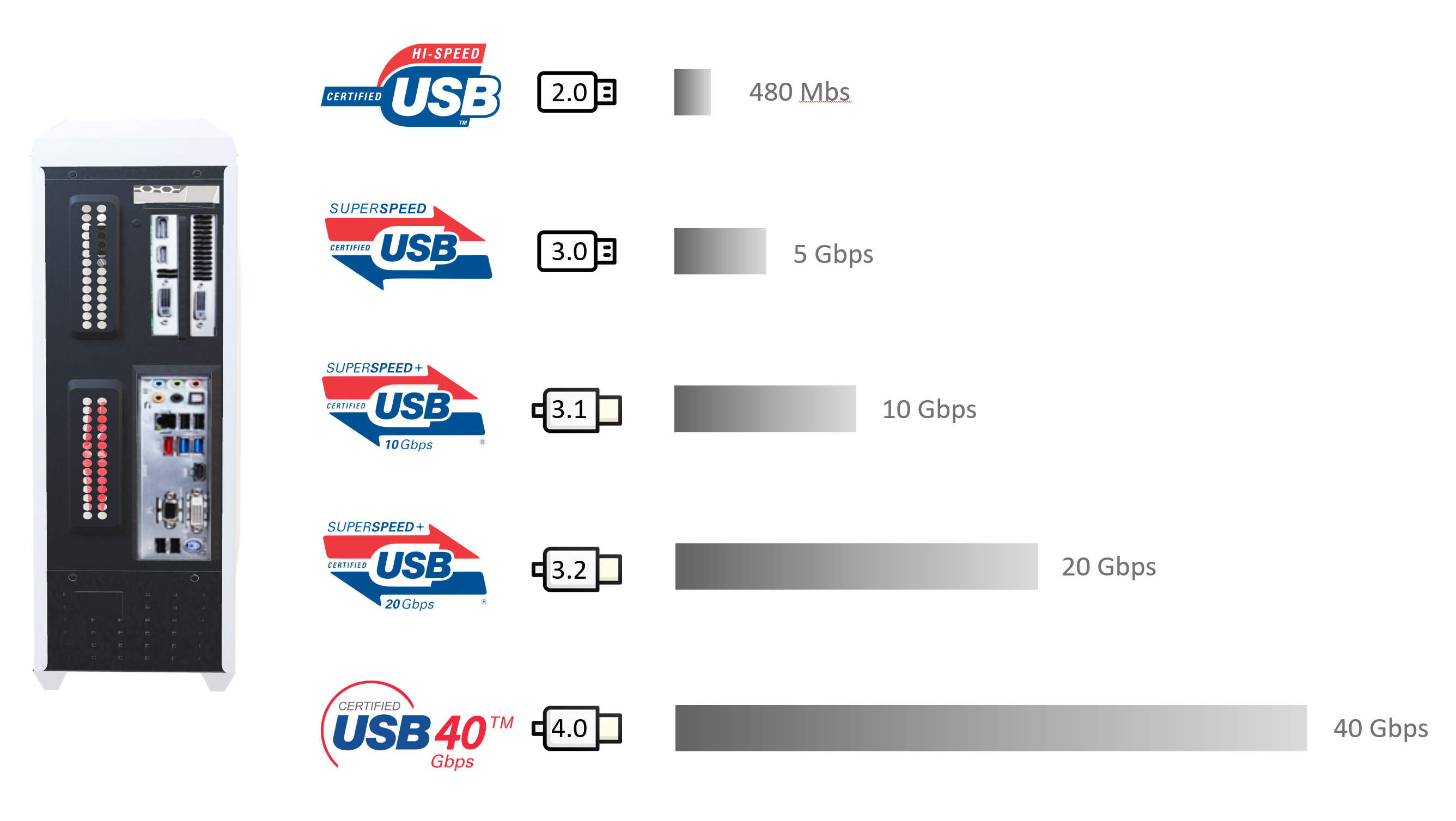

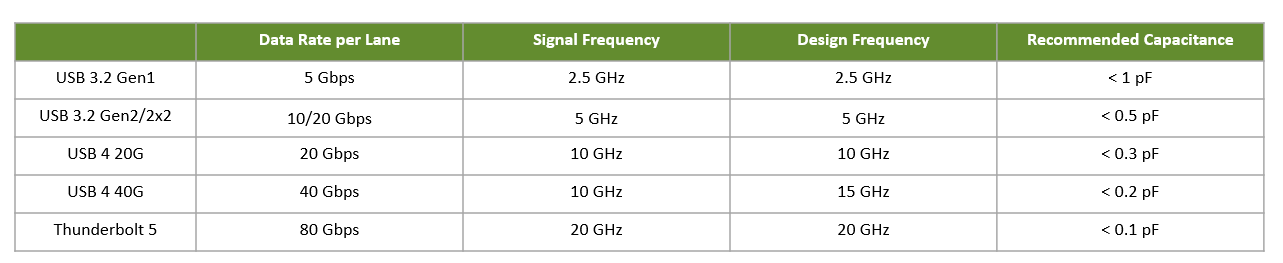

超高速傳輸介面對訊號損耗與空間配置有特定要求,因此必須採用低電容且小型化的元件。

Frequency and capacitance estimation formula:

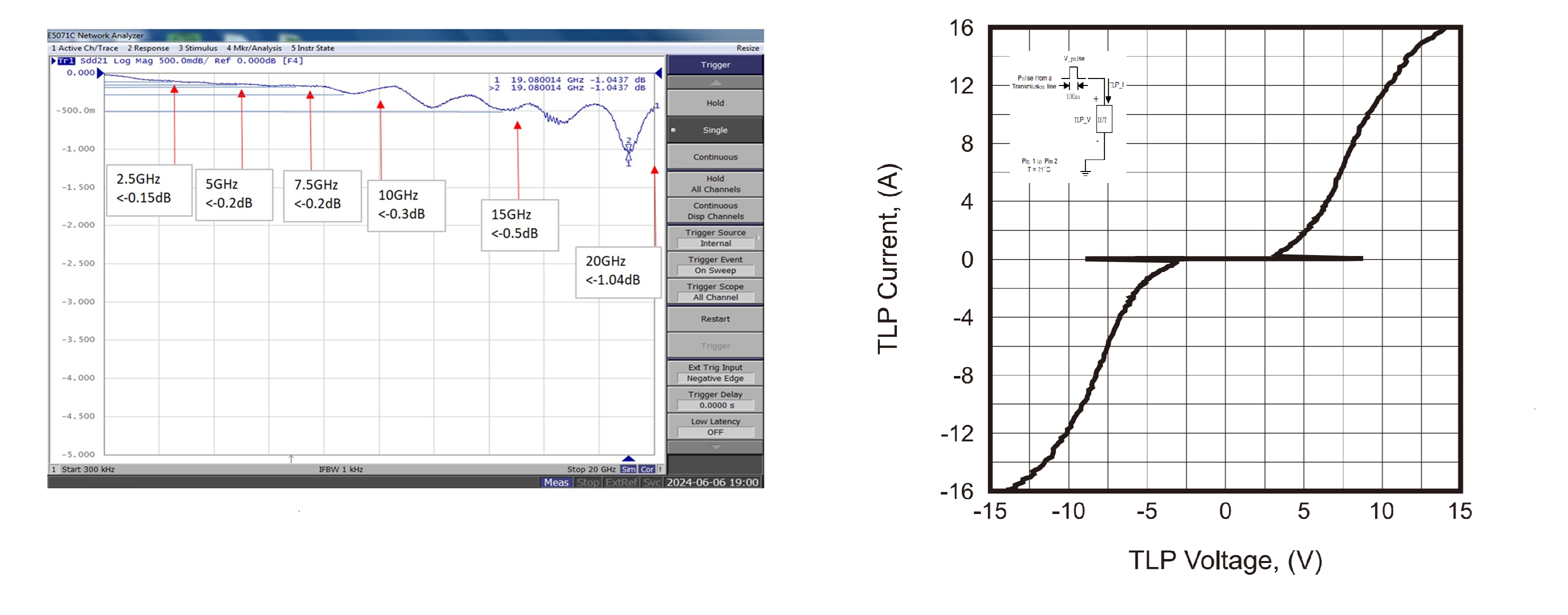

典琦科技 提供 CPDWZ5V0SBP-HF 系列產品,具備更低的箝位電壓與更低的電容值,並針對各類傳輸介面進行最佳化設計。這些元件在眼圖分析與 S21 插入損耗測試中皆展現出優異的效能表現。其中,超低電容型號 CPDWZ5V0P-HF 的電容值低至 0.08 pF。

產品編號

Status

AEC-Q

Uni/Bi

PPP(W)

VRWM(V)

Vc(V)

IPP(A)

Cj(pF)

ESD(kV)

Package

Active

-

Bi

40

5

20

2

0.08

15

CSP0603-2L

Active

-

Bi

20

5

8

2.5

0.15

10

CSP0603-2L

Active

-

Bi

30

5

14

2

0.2

15

0201/DFN0603

Active

-

Bi

14

3.3

3.5

4

0.25

12

CSP0603-2L

Active

-

Bi

72

1.5

8

9

0.26

20

CSP0603-2L

Active

-

Bi

62

5

8.8

7

0.26

15

CSP0603-2L

Active

-

Bi

40

5

8

5

0.29

18

CSP0603-2L

Active

-

Bi

27

5

3.8

7

0.4

26

CSP0603-2L

Active

-

Bi

34

3.3

4.5

7.5

0.45

22

CSP0603-2L

Active

-

Bi

42

5

7

6

0.45

12

CSP0603-2L

Active

-

Bi

75

5

9

10

0.48

16

CSP0603-2L

Active

-

Bi

15

5

5

3

0.5

17

0201/DFN0603-2L

Cookie

本網站使用 Cookie(包括第三方 Cookie)為您提供最佳瀏覽體驗。更多信息,請訪問我們的隱私和 Cookie 政策。繼續瀏覽或關閉此通知,即表示您已接受我們的使用條款。

歡迎您來到「典琦科技」(以下簡稱「本網站」)。

為了確保您能夠安心使用本網站提供的服務和信息,我們特此解釋我們的隱私政策,以保護您的權利和利益。請仔細閱讀以下內容: