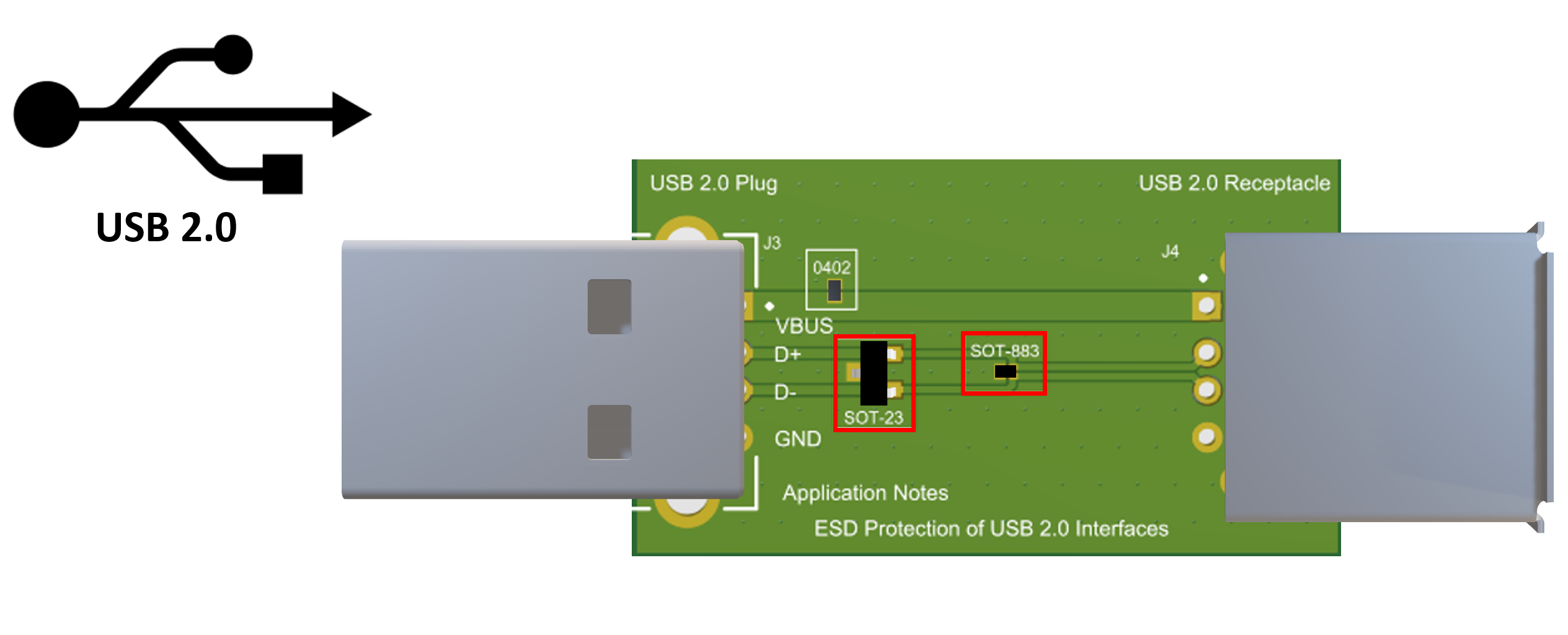

USB 2.0 D+ / D− 線路的 ESD 保護設計指南

1. 差動訊號需要對稱式保護

- D+ 與 D− 為高速差動訊號對,使用 ESD 陣列元件(雙通道或多通道) 可確保各通道具備匹配的保護特性,避免產生訊號不平衡或偏移。

2. 整合式封裝簡化佈線設計

- 陣列型元件(如 SOT-23、SOT-143)可在單一封裝中整合多個通道,不僅節省 PCB 空間,也能有效簡化佈線。

3. 電容匹配以確保訊號完整性

- ESD 陣列元件具備高度一致的通道間電容匹配,典型值約 0.5–1 pF,非常適合維持 USB 2.0(480 Mbps) 的訊號品質。

4. 靠近連接器的緊湊配置

- 小型封裝可將元件配置於 USB 連接器附近,降低寄生電感,進一步提升 ESD 防護效率。