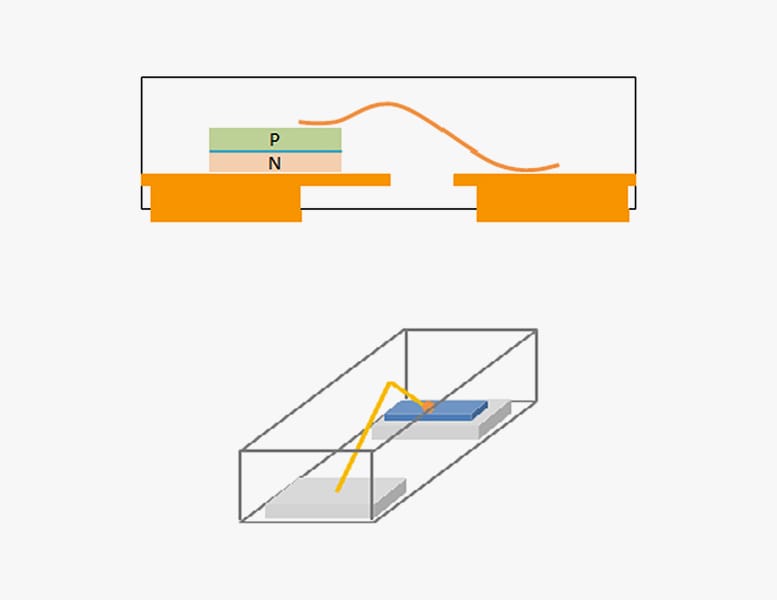

Chip-to-package ratio in wire bonding process

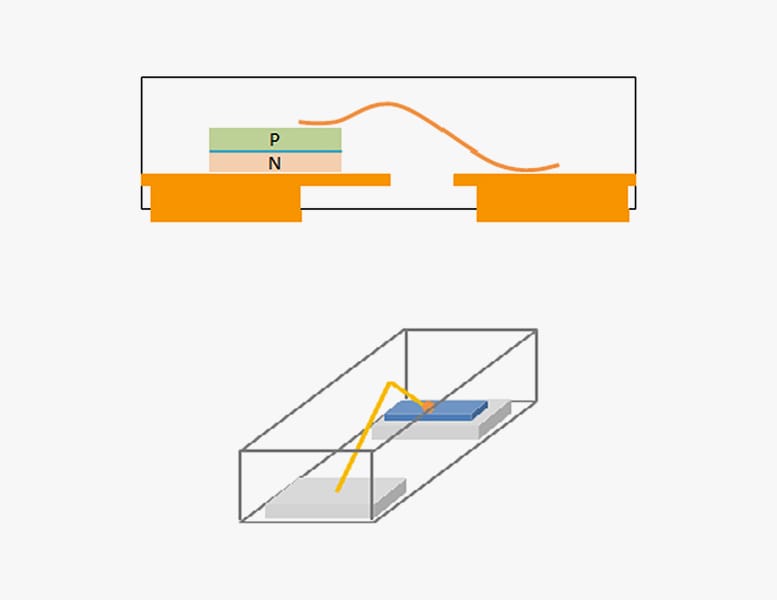

Chip-to-package ratio in WLCSP process

典琦 以WLCSP二極體封裝技術引領超小型電子設備產業。

Chip-to-package ratio in wire bonding process

Chip-to-package ratio in WLCSP process

隨著產品應用和製造流程的演進,傳統的二極體封裝方法,已逐漸無法滿足新一代產品的需求。尤其是在穿帶裝置領域,隨著設計日趨緊湊纖薄,以及對電池效率需求的不斷提高,PCB空間持續縮減,直接影響著元件的選擇。除了性能提升,如今的元件還必須滿足嚴格的尺寸要求,這不斷挑戰著製造流程和產品設計的極限。

典琦科技 長期以來一直是超小型封裝元件開發的領導者,如今更處於製程創新的前沿。該公司推出了一款六面模製WLCSP ESD保護二極管,其最小的01005(0.4 x 0.2 mm)封裝樹立了新的行業標竿。該製程也向上相容,支援0201(0.6 x 0.3 mm)封裝,為採用WLCSP技術開發各種二極體類型鋪平了道路,充分展現了其在更廣泛產品領域的優勢。

傳統二極體生產採用垂直P/N晶片結構,使用原有的封裝方式將陽極和陰極對齊到同一側。由於封裝尺寸的限制,此類封裝中實際晶片尺寸通常小於封裝尺寸的十分之一,從而限制了功率輸出。然而,WLCSP透過在相同封裝尺寸內最大限度地利用晶片來消除這些限制,從而為空間受限的應用提供具有更高功率處理能力和功能性更佳的元件。

PREV.

NEXT

歡迎您來到「典琦科技」(以下簡稱「本網站」)。

為了確保您能夠安心使用本網站提供的服務和信息,我們特此解釋我們的隱私政策,以保護您的權利和利益。請仔細閱讀以下內容: